## Részletes zárójelentés K72611

A kutató munka tervezett ütemtervéhez képest változtatást igényelt a megfelelő dekompozíciós algoritmus kidolgozásának a vártnál hosszabb kutatási időigénye. A pályázat megfogalmazásakor ugyanis feltételeztük, hogy dekompozícióra, mint NP-teljes problémára könnyebben tudunk a céljainknak megfelelő megoldást kidolgozni gráfelméletből és a hardver/szoftver partícionálásból ismert algoritmusok módosítása révén. Az előre megadható szegmens-szám és kapacitás, a kommunikációs időigények, valamint a felhasználandó processzorok főbb tulajdonságainak figyelembe vehetősége az alkalmazott genetikus algoritmus célfüggvényének megfelelő kialakítására vonatkozó kutató és kísérleti munka révén megoldhatónak bizonyult. Ugyanakkor bebizonyosodott, hogy az eredetileg elképzelt módon nem lehet garantálni, hogy a keletkező szegmensek között ne alakulhassanak ki visszacsatolások, azaz formálisan hurkok, ami a teljes módszer hatékonyságát jelentősen csökkentette volna. A szegmenshurkok ugyanis előre nem látható mértékben eleve korlátozták volna a pipeline újraindítási idő előre megadhatóságát a magas szintű szintézis során. Ezáltal a kutatási terv egyik fő célkitűzése és a szakirodalmi eredményekhez képesti egyik legfontosabb újdonsága került volna veszélybe. Ennek a kutató munka során 2010 júniusában felmerült nehézségnek a leküzdése pótlólagos algoritmus-kutatást és kísérleti munkát igényelt. Az ebből fakadó időcsúszás mérséklése érdekében az eredetileg tervezetthez képest több párhuzamos hallgatói és doktoranduszi munkára volt szükség. Mindaddig, amíg nem találtunk megoldást, a részeredményeink nemzetközi konferenciákon történő publikálását nem tudtuk a kutatási tervben elképzelt módon megkezdeni. Fentiekből következően ugyancsak késedelmet szenvedett a teljes kutatási eredményt képező módszer és keretrendszer publikálása rangos nemzetközi folyóiratban. Miután megtaláltuk a megoldást, már célszerűbbnek találtuk, ha erre a folyóiratcikkre összpontosítunk. A megoldás lényege az, hogy az NP-teljes jellegű dekompozíciót megelőzően mindazokat a szegmensképző vágási lehetőségeket szisztematikusan meghatározzuk, amelyek nem okoznak szegmenshurkokat. Ezek közül a vágási lehetőségek közül is csak azokat kapja meg a genetikus algoritmus bemenetként, amelyek szegmensközi kommunikáció szempontjából a legkedvezőbbek. Így a genetikus algoritmus csak ezek közül a kedvező vágási lehetőségek közül tud választani az eredetileg kidolgozott költségfüggvény szerint. A megoldás részletes leírása az 1. Melléklet. "Mapping into a Cutting Matrix (CM)" című fejezetében található. Ez a dokumentum képezte a közvetlen alapját a teljes kutató munkát összefoglaló azonos című publikációnknak, amelyet a szűkebb szakterület egyik legrangosabb folyóiratához (ACM Transactions on Design Automation of Electronic Systems) küldtünk meg 2012. szeptember 19-én. Jelenleg bírálati szakaszban van.

(Thank you for your recent manscript submission to ACM TODAES.

The Editorial Assistant will shortly transmit your paper to the Editor-in-Chief, who then assigns it to an Associate Editor. (If the paper is a revision of a previously submitted paper, it will automatically be assigned to the previous Associate Editor.)

The Associate Editor will be responsible for handling the review process for your paper -- and should be your primary point-of-contact for any questions you may have regarding your submission and the review process. Once the AE has been assigned, you will be able to locate their name and contact information on the website under "Status".

Please refer to your paper number in any future correspondence.)

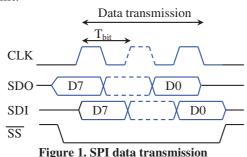

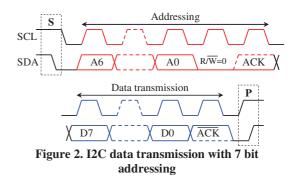

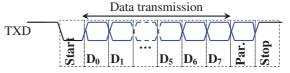

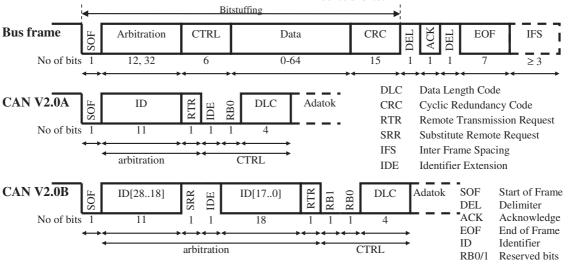

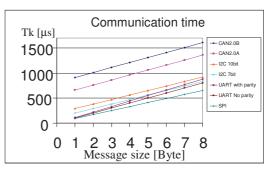

Amint az a kutatási tervben és a részjelentésekben is hangsúlyozottan szerepel, a célul kitűzött módszer és keretrendszer meghatározó része a dekompozíciós eljárás, amelynek egyik újnak tekinthető eredménye a kialakuló szegmenseket megvalósító processzor egységek közötti kommunikáció előzetesen becsült időigényének a figyelembe vehetőségének módja a dekompozíció során. Ez különösen fontos olyan célrendszerekre történő alkalmazások esetén, amelyekben a processzorok közötti információcserének valamilyen szabványos sínrendszeren kell történnie. Ilyenkor nagy segítség a tervezés során, ha a különböző leggyakrabban

alkalmazott sínrendszerekre egységes becslési módszer áll rendelkezésünkre. A becslési módszerrel kapcsolatos vizsgálatainkat és eredményeinket foglaltuk össze a **2. Mellékletben** leírt cikkben, amelyet 2012. október 12-én küldtünk a Periodica Polytechnica folyóirathoz, ahol jelenleg bírálati szakaszban van.

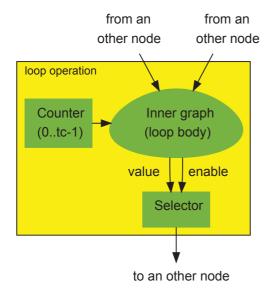

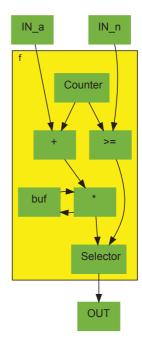

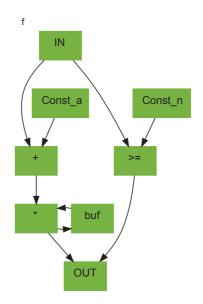

A kutatás eredményeként kifejlesztett tervező keretrendszer hatékonyságát jelentős mértékben befolyásolja a megoldandó feladatot leíró programban lévő ciklusok kezelésének módja a magas szintű szintézis fázisában. A tervező rendszerünk jelenlegi változatában a ciklus-kezelésnek egy egyszerú könnyen megvalósítható módját alkalmaztuk. Nyilvánvaló azonban, hogy a ciklusok lappangási idejének csökkentése révén csökkenthető a rendszer pipeline újraindítási idejét korlátozó hatás. A cikluskezelés algoritmusának kifejlesztése szerepel a jelen kutatás folytatási céljai között is. Ezzel kapcsolatos a **3. Melléklet**, amelynek alapján folyóiratcikket készítünk elő.

A kísérleti példákon és benchmark-feladatokon kiértékelt rész-algoritmusokon kívül a kutatási tervben célul tűztük ki, hogy az elkészült tervező keretrendszert meglévő, lényegében intuitív módon kialakított többprocesszoros rendszerek újratervezése révén is összehasonlító értekelésnek vetjük alá. Ilyen meglévő rendszernek a

[1] GORACZKO, Michel ; LIU, Jie ; LYMBEROPOULOS, Dimitrios ; MATIC, Slobodan ; PRIYANTHA, Bodhi ; ZHAO, Feng ; FIX, Limor (Bearb.): Energy-optimal software partitioning in heterogeneous multiprocessor embedded systems.. In: *DAC* : ACM, 2008. - ISBN 978-1-60558-115-6, p-p. 191-196

[2] M. Brandstein and H. Silverman. A robust method for speech signal time-delay estimation in reverberant rooms. In ICASSP, page 375. IEEE Computer Society, 1997.

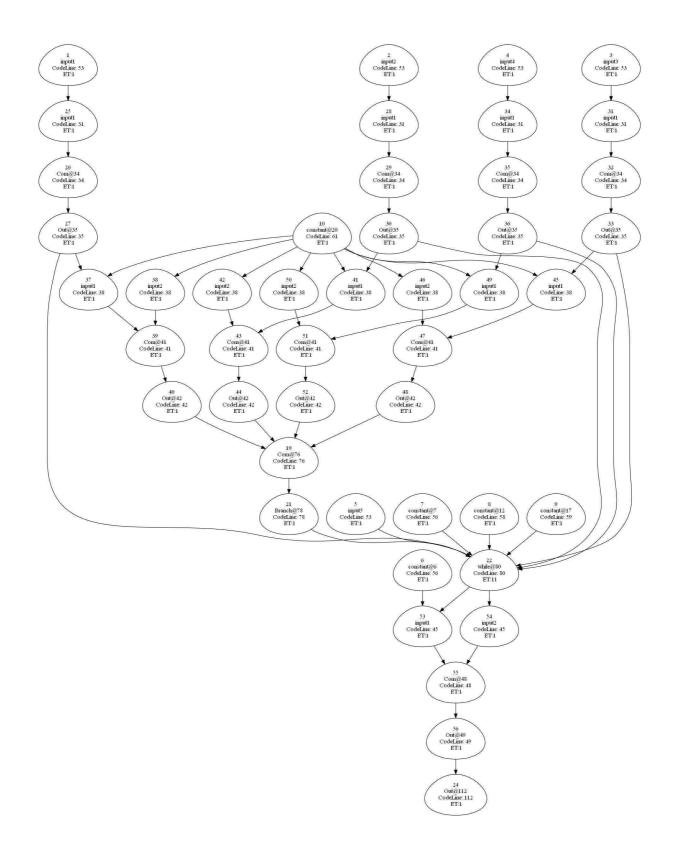

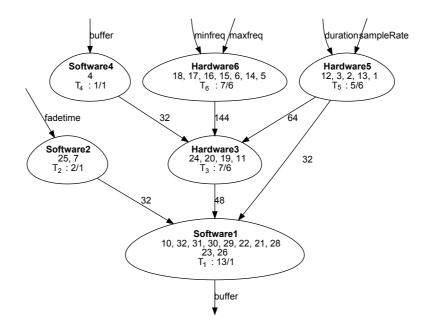

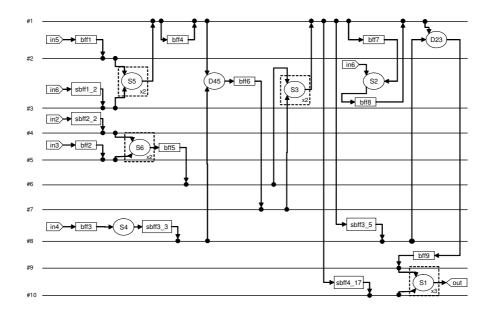

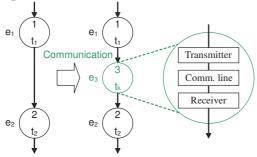

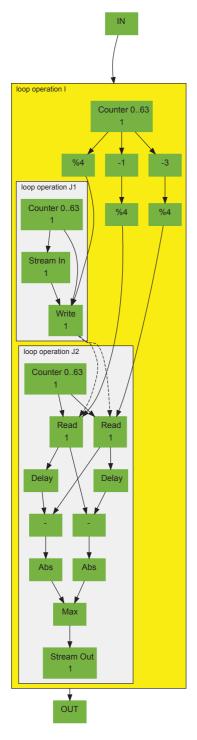

publikációkban leírt, hangforrás lokalizációt megoldó rendszert választottuk. A feladat C nyelvű leírásából az alábbi adatfolyam gráfot (SHSDG) generáltunk.

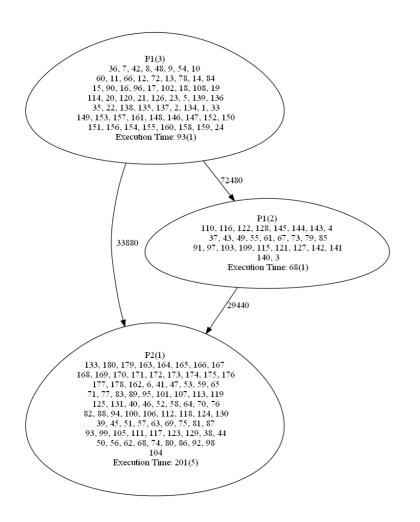

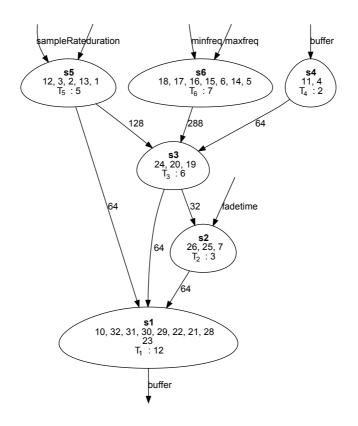

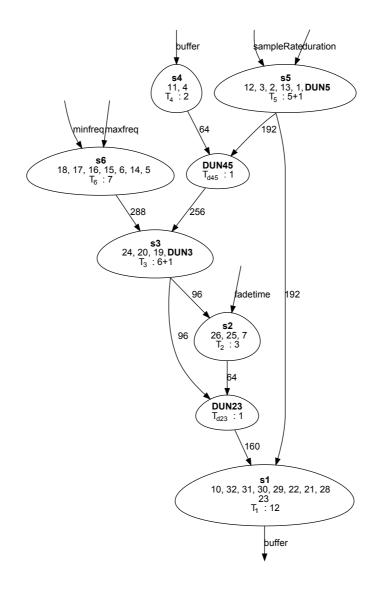

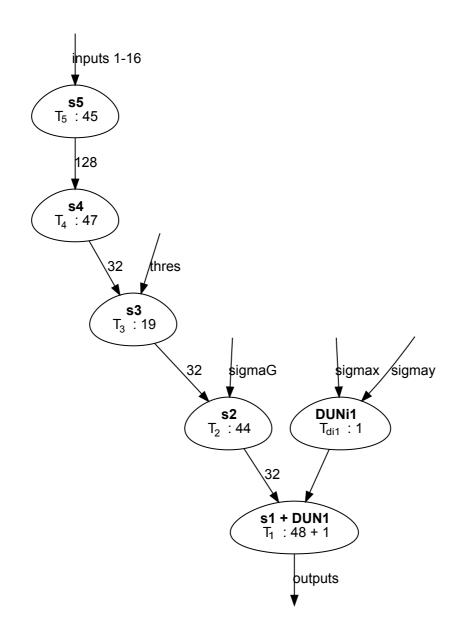

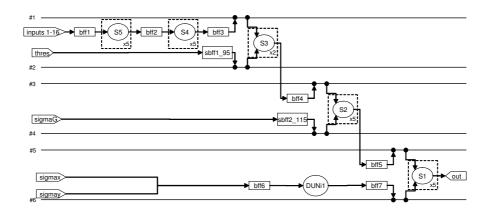

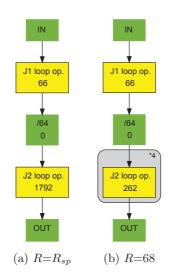

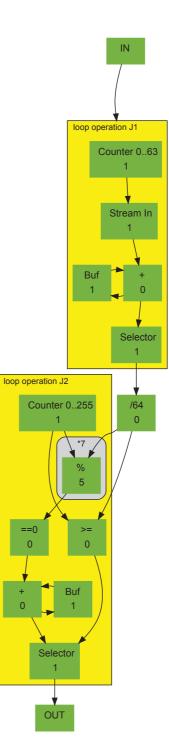

Mivel a feladat sok fix iterációs számú hurkot tartalmaz, ezeket egy előfeldolgozó segítségével "kiterítettük". Az így módosított SHSGH az iterációs hurkok megszüntetése révén jelentős mértékben elősegíti a párhuzamos végrehajtást és a pipeline szervezést. A dekompozíciós eljárásunk eredményeként az alábbi, az eredeti megvalósításhoz [1] hasonló eredményre jutottunk.

Ebből a megoldásból kiindulva azonban még a keretrendszerünk részét képező PIPE magas szintű tervező eszköz segítségével nagyobb átbocsátási képességű pipeline feldolgozás alakítható ki az előre megadható kívánt újraindítási időre való tervezés révén. Néhány ehhez hasonló újratervezési feladat befejezése után az eredményekből levonható következtetések alapján folyóiratcikket készítünk elő.

Budapest, 2012. november 26.

\_\_\_\_\_

Dr. Arató Péter az MTA rendes tagja Kutatásvezető

# 1. Melléklet

## Synthesis of a Task-dependent Pipelined Multiprocessing Structure

P. Arató<sup>\*</sup>, D. A. Drexler, G. Kocza, G. Suba

July 24, 2012

#### Abstract

This paper presents a method for designing a special multiprocessing structure for making the pipeline function possible as a special parallel processing even if there is no efficiently exploitable parallelism in the task description. The starting point of this synthesis method is the task description assumed to be given by a program written in a high level language (e. g. C, Java, etc). The next step is a decomposing algorithm for generating proper segments of the task-describing program. The desired number of the segments and the main properties of the processor set implementing the segments can be given as input parameters for the decomposition algorithm. The estimated communication time-demand is also taken into consideration. For constructing a beneficial pipeline structure, the high-level synthesis (HLS) methodology of pipelined datapaths is applied. The HLS methods attempt to optimize by executing the scheduling and allocation steps applied on the task-oriented input dataflow graph generated from the graph of the segments produced by the decomposition. Therefore, the resulted multiprocessing structure is not a uniform processor grid, but it is shaped depending on the task to be solved, i.e. it can be called a task-dependent multiprocessing or multi-core structure. In order to show the whole method as a framework, a specific HLS tool is applied, which generates an optimized simple arbitration-free bus system between the processing units. In this structure, there is no need for extra software to organize the communication, if the processing units can transfer input-output data directly. For illustrating and evaluating the method, the step-by-step solution is shown for two tasks as experimental results.

*Keywords:* program code decomposition, pipelined multiprocessor systems, high-level synthesis hardware/software co-design, system-level synthesis

<sup>\*</sup>Budapest University of Technology and Economics, Department of Control Engineering and Information Technology, H-1117, Budapest, Magyar tudósok krt 2., IB321, Phone: +36-1-463-2196, emails: arato@iit.bme.hu, drexler@iit.bme.hu, koczagbr@gmail.com, sugergo@iit.bme.hu

## 1 Introduction

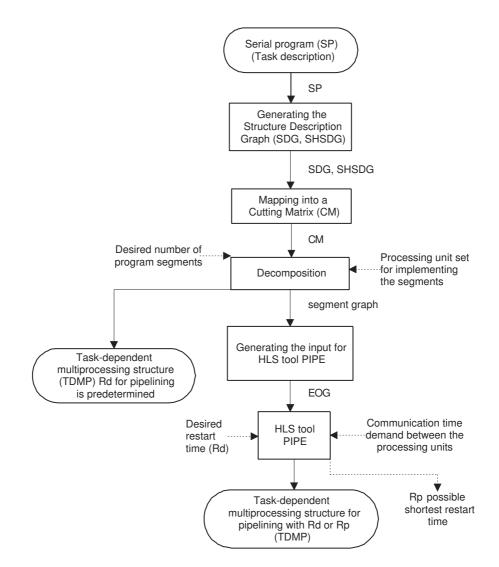

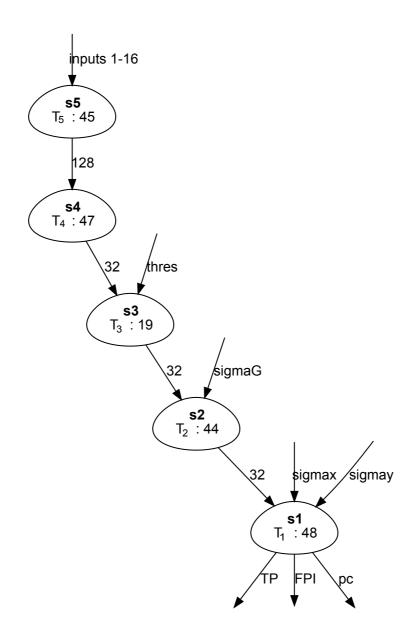

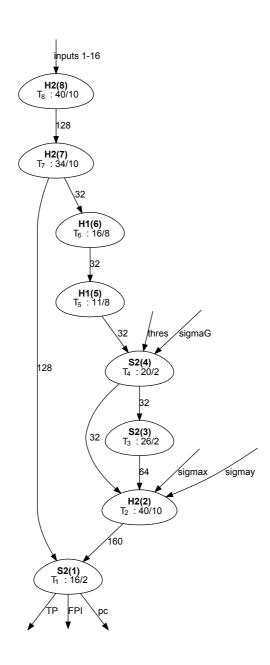

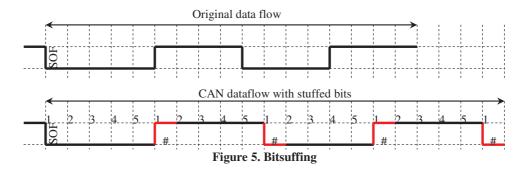

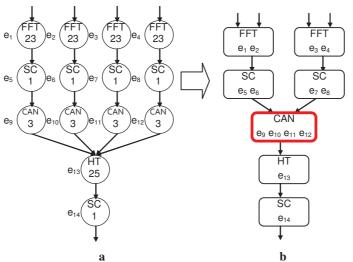

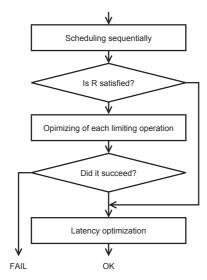

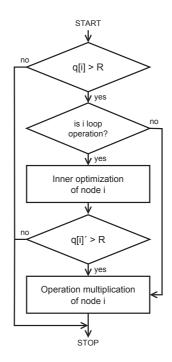

If a task-describing program has no efficiently exploitable parallelism (it can be called an *essentially serial* or a *sequential one*), then speeding up its execution would not be efficient by applying a uniform parallel processing architecture. In such cases, the execution speed could be increased by applying a higher performance single processing unit, but this would still exclude pipelining to speed up processing large amount of data. However, many practical tasks require and can capitalize the pipelining which is a special case of parallel processing. For constructing a beneficial pipeline structure, the high-level synthesis (HLS) methodology of pipelined datapaths can be applied. Based on proper decomposed parts (segments) of the serial program, a dataflow-like graph representation can be formed as the input for a HLS tool. Depending on the desired pipeline throughput (in other words: on the desired value of the restart time determined by the frequency of being able to receive new input data), the HLS methods attempt to optimize by executing the scheduling and allocation steps applied on the task-oriented input dataflow-like graph generated from the graph of the segments produced by the decomposition. Therefore, the resulted multiprocessing structure is not a uniform processor grid, but it is shaped depending on the task to be solved by the initial serial program, i.e. it can be called a task-dependent multiprocessing or multi-core (TDMP) structure designed for pipelined data processing. In Figure 1, the main design steps of the whole method are illustrated as a framework. In the first step, a Sructure Description Graph (SDG) is generated from the serial task-describing program (SP). In this paper, it is assumed that SP is written in programming language C. By choosing another high level language for task-description, the SDG generating step may be affected, but the whole design method as a framework remains applicable. As the SDG represents all hierarchy levels of SP, a reduced SDG is formed by restricting it to a single (usually to the highest) hierarchy level. Based on this Single Hierarchy Level SDG (SHSDG), a mapping algorithm is presented for constructing a *cutting matrix* (CM) to designate all such allowable cutting places which may result in beneficial segments by the decomposition. A cutting place in the SHDSG is considered not allowable, if it would cause a loop in the graph formed by the segments as nodes. The decomposition (i.e. an advantageous selection from the allowable cutting places) for generating the segments is then performed by applying a genetic algorithm. The desired number (P) of the resulting segments can be given as an input parameter for the decomposing algorithm. The main properties of the available set of processing units for implementing the segments and the communication time-demand can also be taken into consideration during the decomposition and in selecting from the set of processing units given in advance. The selected processing units and the communication structure between them represent already a TDMP structure enabling also the pipeline function. However, the throughput (i.e. the applicable shortest pipeline restart time) is predetermined by the properties of the processing units implementing the segments and by the communication time between them. To increase the throughput (i.e. to decrease the applicable shortest pipeline restart time), an HLS tool may be used by forming its dataflow-like input graph based on the segments as nodes. In this case, the segments are not assigned to processing units before having the result generated by the HLS tool. In order to show the whole method, the specific HLS tool PIPE [1] is applied in this paper, but other tools could be substituted by modifying the input graph, if it is necessary. The output of this HLS tool is a structure consisting of redefined and replicated processing units communicating on a simple arbitration-free bus system. In this structure, there is no need for extra software to organize the communication, if the processing units can transfer input-output data on the buses directly. The desired value of the restart time  $(R_d)$  can be given as an input parameter for the HLS tool PIPE. If the constraints caused by the communication time-demand or loops exclude applying  $R_d$ , then the shortest possible restart time  $(R_p)$  can also be calculated and implemented by PIPE. For illustrating and evaluating the whole synthesis method the step-by-step solution of two task is shown as experimental results. The modularity of the method permits that some algorithms developed and demonstrated in this paper (decomposition, forming the input for the HLS tool and the tool PIPE itself) may be replaced by other algorithms and tools depending on the properties of the target system and on the special requirements of the application.

The remainder of this paper is organized as follows. As the crucial part of the proposed method is to find a proper segmentation of the initial program SP, Section 2 summarizes some related works in the field of program decomposition. Section 3 presents the basic rules for generating the structure description graphs (SDG and SHSDG). In Section 4 the mapping algorithm for constructing the cutting matrix (CM) is described as a preprocessing step for the decomposing algorithm. The proposed genetic decomposing algorithm is presented in Section 5. In Section 6, experimental results demonstrate the whole method by solving two tasks step-by-step. On these examples it is shown how to modify the graph of segments for generating the input of the HLS tool PIPE. The resulting TDMP architectures and the arbitration-free simple bus systems provided by the extended version of PIPE are also illustrated in this section. Conclusion and further research are summarized in Section 7.

## 2 Related Work

The TDMP architecture can be considered as the nearest approach to the application-specific multiprocessing structures (ASMP) [2], [3], [4], where the properties of the processing units and the communication time between them are taken into consideration essentially with intuition by analysing the task. Thus, the selection from the available processing units and the task assigning to them are not algorithmized. The desired pipeline restart time is also not an input parameter in the ASMP design. Since this paper aims to present a method for designing a TDMP structure by performing the above synthesis steps as far as possible algorithmically already in the task distribution phase, therefore the most comparable related research results are in the fields characterized by pro-

Figure 1: The main steps of the method

gram decomposition, program slicing, code segmentation and special splitting algorithms in hardware-software co-synthesis. In this paper, the decomposition -as the base of the synthesis method- fulfills the requirements as follows:

- The task describing program is assumed to be basically serial (sequential) i.e. efficiently exploitable parallelism is not necessarily found in it.

- The desired number of code segments resulting from the decomposition can be given in advance and the effect of fewer segments can also be evaluated.

- The available set of processing units and the main properties of them can be taken into consideration in the decomposition algorithm.

- From the resulted graph of segments, the input to a HLS tool can be generated in formal steps.

In the following overview, the above requirements are also considered. There is a wide spectrum in the literature of separating a program code into segments on various purposes. Program slicing is usually used for debugging, program analysis, program understanding, code reusing, software maintenance, program integration, program differencing etc., as shown in [5, 6, 7]. The algorithms of program slicing do not necessarily result in an executable program. Program distribution covers the disassembling of a program and reassembling it in another way preserving its executability and functionality. For example, in reverse engineering [8], this method can be applied to increase the software performance [9] by changing the execution order of the software segments. In the field of hardware-software partitioning, the aim is to improve the performance by implementing the separated parts in software and hardware units respectively [10, 11, 12, 13, 14, 15, 16, 17].

Most of the methods start with a graph representation of the program to be decomposed. The graph representation idea comes from Ottenstein [18, 19] by introducing the program dependence graph. There are very few solutions which mention the way how the graph representation is made from the program to be decomposed. One of the few examples is [13], where the method of [20] is applied for graph generation and the input of the algorithm can be a program written in C, C++ or SpecC. Besides, [13] puts emphasis on finding parallelism in the code, but there is no way to specify the number of the segments or the properties of the processing units. Many program distribution algorithms attempt to find exploitable parallelism. Busherian [8] uses an actor model of the object oriented program, and looks for concurrency among actors by instruction scheduling without considering the properties of the units or the desired number of the segments. Hoffmann et. al. [21] pointed out that parallelizing can be achieved by finding spatiotemporal patterns in the code. They apply task and data partitioning in time and space. Influencing the number of resulting segments is not aimed. Johnson et. al. [22] parallelize the program along its threads and apply a min-cut based algorithm for finding the nearly optimal distribution of the task graph. It is possible here to give the set of the processing

units, but the desired number of segments is not a parameter. Knudsen et. al. [12] support the procedure of hardware-software co-design by decomposing into hardware and software parts. Their dynamic programming algorithm aims to minimize the hardware area with a global execution time constraint, and the execution time with a total hardware area constraint. The algorithm detects the non-overlapping sequences. The properties like execution times, communication times are estimated, and exploiting the parallelism in the code is also targeted. Deniziak [23] aims to find the cheapest system architecture satisfying the given time constraint. Execution times and system costs can be given or estimated. The method starts from the program architecture and applies the iterative improvements of the sub-optimal solutions to gain processing speed with time constraint. Watson et. al. [10] exploit parallelism by considering the switching cost between the units and solving a multistage optimization problem. The set of the target processing units can be given. Subramanian et. al. [24] look for parallelism by using a compiler controlled program analysis. Their method is very efficient, but the result is based basically on finding exploitable parallelism. In contrary, Spacey et. al. [25] aim to start from a program without any exploitable parallelism and to give the set and the properties of the target processing units. The number of segments is obtained as a result also in this case. Wolf et. al. [11] and Mann et. al. [26, 27, 28] focus on the desired number of segments. Wolf et al. start from a system graph and reduce the number of nodes only if it is necessary to obtain the given time constraint. The properties of the processing units can also be given. Thus, these methods are the nearest approach to the basic objectives of the method presented in this paper.

## 3 Generating the Single Hierarchy Level Structure Description Graph (SHSDG)

For constructing the SHSDG, the structural arrangement of the task-describing program SP is to be analyzed. Let the elements of the program structure be called modules. Modules can be statements, function calls or control structures (e.g. 'if' condition, 'for', 'while' loops, etc.) in the program.

Modules can be divided into two groups: *separable* or *not separable* ones. A module is considered not separable, if it does not contain any other modules or it is a loop. Modules contained by the standard library in the high level programming language applied for SP (e.g. operator '=', any mathematical operation, etc.) are also handled as not separable ones even if it contains other modules. Otherwise, the modules are handled as separable ones.

Modules are executed one by one essentially after each other in a basically serial (sequential) program. This sequence of modules represents an *execution* order. Modules are connected by data links. By observing the data links step-by-step from the inputs to the outputs of the program, a *data passing order* can be defined. The data passing order and the execution order can be different. In the data passing order feedbacks can occur. A feedback is the data passing order

leading back to the input of a module already passed. Feedbacks are always inherent parts of a loop.

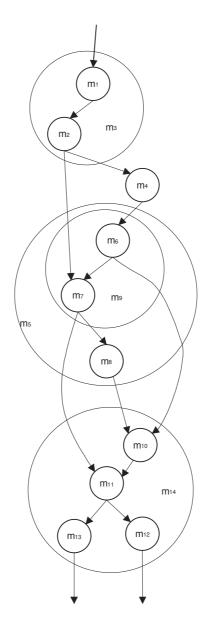

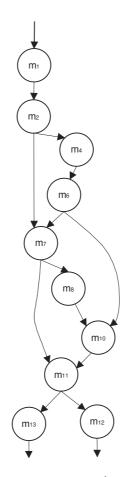

As a result of the program decomposition, *segments* are to be generated. A *segment* is a set of program modules which are assigned to a common processing unit (e.g. software or hardware). Based on the above definitions and considerations the Structure Description Graph (SDG) can be constructed for an SP. In Figure 2, the SDG of a hypothetical SP is shown as an example. Arrows represent the data links and nodes represent the modules among which both separable and not separable ones occur. Modules  $m_3$ ,  $m_5$ ,  $m_9$ ,  $m_{14}$  are separable, because

$$d(m_3) = \{m_1, m_2\}$$

$$d(m_5) = \{m_8, m_9\}$$

$$d(m_9) = \{m_6, m_7\}$$

$$d(m_{14}) = \{m_{10}, m_{11}, m_{12}, m_{13}\},$$

where  $d(m_i)$  denotes the set of modules that are directly called in  $m_i$ , i.e. the set of the direct sub-modules of  $m_i$ . For example,  $m_7$  is also a sub-module of  $m_5$ , but not a direct one. If  $d(m_i)$  is not separable, then formally  $d(m_i) = m_i$  can be written. In this sense,  $m_1, m_2, m_4, m_6, m_7, m_8, m_{10}, m_{11}, m_{12}, m_{13}$ , are not separable. If the set  $d(m_i)$  contains  $m_k$ , then  $m_i$  is the direct host module of  $m_k$ , formally:  $h(m_k) = m_i$ . In Figure 2:

$$\begin{array}{lll} h(m_1) &=& h(m_2) = m_3 \\ h(m_8) &=& h(m_9) = m_5 \\ h(m_6) &=& h(m_7) = m_9 \\ h(m_{10}) &=& h(m_{11}) = h(m_{12}) = h(m_{13}) = m_{14}. \end{array}$$

If  $m_i$  has no direct host, then formally  $h(m_i) = m_i$  can be written. In Figure 2:

$$h(m_3) = m_3$$

$h(m_4) = m_4$

$h(m_5) = m_5$

$h(m_{14}) = m_{14}$ .

Based on the relations d(m), h(m) and on the data passing order, hierarchy levels  $(H_n)$  can be defined. The first hierarchy level  $(H_1)$  consists of the set of modules, for which  $h(m_i) = m_i$ . The *n*-th hierarchy level  $(H_n)$  consists of the set of modules determined by the union of all sets  $d(m_i)$  for all  $m_i$ -s on the (n-1)-th hierarchy level. Formally:  $\bigcup_{n=1} [d(m_i)]$ , where  $\bigcup_{n=1}$  denotes the union of the sets on the n-1-th hierarchy level.

In Figure 2, the hierarchy levels are as follow:

$$\begin{array}{rcl} H_1 & : & \{m_3, m_4, m_5, m_{14}\} \\ H_2 & : & \{m_1, m_2, m_4, m_9, m_8, m_{10}, m_{11}, m_{12}, m_{13}\} \\ H_3 & : & \{m_1, m_2, m_4, m_6, m_7, m_8, m_{10}, m_{11}, m_{12}, m_{13}\} \end{array}$$

Figure 2: A Structure Description Graph (SDG)

According to the above definition,  $H_3$  is the highest hierarchy level, because further separable modules do not exist. It is obvious that the number of modules on the n-th hierarchy level is always greater than or equal to the number of modules on the (n-1)-th level  $(|H_n| \ge |H_{n-1}|)$ . Besides the hierarchy levels, generally other sets of modules may exist, which also represent correct data passing orders. For example, the set  $\{m_1, m_2, m_4, m_6, m_7, m_8, m_{14}\}$ , represent a correct data passing order, but it is a mixture from different hierarchy levels. If the decomposing algorithm requires checking each data link in the SDG for attempting to find the optimal cutting places in creating the segments, then the calculations should be executed obviously on the highest hierarchy level. Otherwise, some data links would be hidden from checking and evaluation. However, there might be such special requirements or limitations that prefer to consider lower (even mixed) hierarchy levels in checking the data links. As the SDG represents all hierarchy levels of SP, a reduced SDG can be formed by restricting it to the desired single (usually to the highest) hierarchy level. The decomposing algorithm performs separating the modules into segments based on this Single Hierarchy Level SDG (SHSDG). For example, an SHSDG generated from the SDG in Figure 2 for the  $2^{nd}$  hierarchy level is shown in Figure 3.

In this paper, the SP is assumed to be written in C language as an example. Although, the SP could be written in another imperative or functional language (e.g. Java, Haskell, Erlang), it is focused only on C in the next section by presenting a specific method how to generate the SHSDG from SP.

#### Generating the SHSDG from C code

The GNU Compiler Collection (GCC) is a widely used open source compiler from C to machine code. This compiler can be applied for making the generating procedure easier. The compiler has three main parts: the frontend receiving the C source code and producing an intermediate representation (IR) called *Generic* [29], the middle end producing the register-transfer language (RTL), and the backend producing the desired machine code for the target CPU. It is advantageous to use a reduced subset of the Generic IR, called GIMPLE [29], where the expressions are given in a *single-static assignment (SSA)* form [30]. The reasons of this choice are as follow:

- Using the GCC is beneficial in any case, because the difficult processing of the source code can be performed automatically without any additional efforts (compiler steps: lexer, parser, syntax-analyses, and AST creating).

- The RTL would provide already a hardware-based representation, but this hardware would always be a CPU, which would be a very strict limitation.

- The Generic (the output of the frontend) is the first language independent IR, but it is not simple enough, because a large amount of so called *syntactic sugar* still remains in the code.

- Therefore, GIMPLE as the simpler IR seems to be more beneficial to use.

Figure 3: The SHSDG generated on the  $2^{nd}$  hierarchy level of the SDG in Figure 2

The GIMPLE code consists of the same C functions as the source code. The functions are divided into blocks. Every block is an acyclic dataflow graph, and inside a block there are no control flows, the expressions can be evaluated just considering the data dependency. However, a control flow cannot be avoided for determining which block should start in each situation. At completing the execution of a block, it is always determined which block should start. Therefore, control lines appear between the blocks besides data links.

In GIMPLE, the function headers have the same parts as in C (return type, name and parameter list). The function bodies begin with the local variable declarations followed by the *GIMPLE instructions* [31]. The translations of these language elements will be discussed in the following.

The elements of the function parameter list are handled as virtual input nodes (modules). The advantage of these virtual nodes is that the interfaces of a module can be determined easily from the SHSDG model. Moreover, if an input parameter is used by more than one expression, a virtual input node can ensure that only one data link goes into the module (node) representing the input parameter. The outputs of functions (and of the program as well) are also handled as virtual nodes. This guarantee that the output nodes of the graph will have only such outputs that point out of the graph. This feature will be beneficial for the cutting matrix generation algorithm described in Section 4. The execution time of the virtual nodes could be 0, but the tool PIPE [1] can not handle the zero duration time. Therefore, the execution time of these virtual nodes is assumed to be 1. Of course, this causes a minimal increase in the latency, but the pipeline restart time is not affected.

All local variables will be converted to data links between modules (these will not generate any modules at all).

The most of the considerations during the translating procedure are required by the GIMPLE instructions. The correspondence between the SHSDG elements and the GIMPLE instructions are as follows:

- gimple\_label: it defines a block in the GIMPLE code, and a block is translated into a separable module (the GIMPLE instructions inside a block require the same handling).

- gimple\_goto: it is a jump instruction appearing in the case of a loop, branch or an explicit goto element of a C code. The direction of the jump can be forward or backward (a backward jump goes to a source code line that it has processed before, and the jump is forward otherwise). A backward jump results always in a loop (for, while, etc.) handled as a not separable module, because the current version of the applied HLS tool PIPE can not handle the separation of the body of a loop.

- gimple\_assign: it represents atomic operations (+, -, \*, <), therefore not separable module is to be generated in SHSDG.

- gimple\_cond: it represents a branching condition evaluation, and it determines the next block to start. It is an atomic operation translated into a not separable module in SHSDG.

- gimple\_phi: it refers to joining the outputs of different blocks. The translation of this instruction results in a not separable multiplexer (MUX) module [1] in SHSDG.

- gimple\_call: it represents a function call. The function can be user defined or a part of a library. A user defined function is translated into a separable module in SHSDG by inlining. A library function is translated into a not separable module in SHSDG.

- gimple\_return: it is the last GIMPLE instruction of a function. The translation into SHSDG results in a virtual output node similarly to the virtual input node discussed earlier (the execution time is also 1 here).

Since the SP is assumed to be written in C language, it is not necessary to bother with the following C++ or assembly-related elements of the GIMPLE structure (e.g. gimple catch, gimple try, and gimple asm).

The main advantage of the GCC-supported generating method is that there is no need to deal with the C source code. Thus, it is not necessary to handle language elements that are difficult to process: macros, header files, various syntactic sugars (for cycle, do-while cycle and some special operators e.g. ".", etc.).

Nevertheless, two very important C language elements, the pointer and the global variables have to be mentioned. A pointer used in a function parameter list represents a pass by reference argument. Therefore, this situation should be represented by applying two data links in the SHSDG: one for the input and one for the output direction. A pointer can refer to a statically or a dynamically allocated memory. In this paper, the dynamical case cannot be handled since the size of the referenced memory block cannot be derived in compile time, but this information should be known for calculating the communication cost for the algorithm in Section 5. Thus, avoiding the pointers with dynamical memory reference is a restriction in writing the SP. Pointers referenced memory block can be derived in compile time, but size of the referenced memory are allowed, because the size of the referenced memory block can be derived in compile time according to the pointer analyses techniques [32, 33, 34].

The other problematic elements, the global variables can be removed by applying the variable-classification step described in [35].

#### Handling of conditional branches

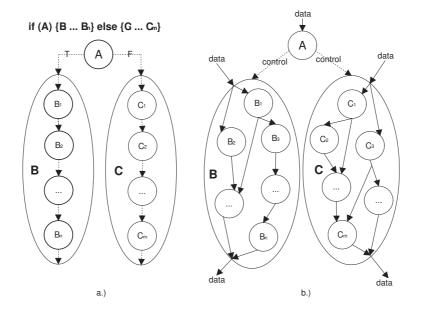

For the modules in the branches, the data passing order cannot be specified by the data links only. Obviously, the actual values on the control lines also influence the data passing order. Therefore, the control lines produced by the condition calculation are also to be taken into consideration besides the data links for handling the conditional branches as separable modules during generation of the SHSDG.

The influence of the control lines on the data passing order can be illustrated by the *control-flow graph* (CFG). The CFG of a conditional branching is shown in Figure 4. a., where dotted arrows represent only the control lines prescribing the control-flow precedence of the modules. The condition evaluation (A) module (gimple\_cond) and the modules in the branches ( $B_i$ -s and  $C_i$ -s) constitute the module set of the conditional branch. In Figure 4. a., only the execution order of the modules is indicated by the dotted arrows. The correspondence between the CFG and the SHSDG is illustrated in Figure 4. b., where only the assumed data passing order is indicated between the modules. The control lines (dotted) from A to all of the modules in B and from A to all of the modules in C have to be added as additional single bit data links in the SHSDG. These additional data links are not indicated in Figure 4. b. in order to maintain the simplicity of the figure. In SHSDG generation, these single bit data links are to be handled as additional input data to each module of the conditional

Figure 4: The control flow graph and the SHSDG of the conditional branches; a.) the control of "if" conditional branch b.) SHSDG substitution of "if" control structure

branches in order to activate its operation. These extra single bit data links can ensure the aternative execution of the branches, what may be beneficial in the allocation phase of the HLS tool.

There may be statements in the SP which are not involved in any kind of data passing only in precedence. Such statements are for example printing statements. In such cases, the control links are also considered formally as single bit activating data links when generating the SHSDG.

## 4 Mapping into a Cutting Matrix (CM)

The aim of the decomposition is to construct the decomposed parts of the program by distributing nodes of the SHSDG into segments. During the distribution, efforts have to be made for forming a structure having only one way communications between the resulted segments. It is important, because bidirectional data links in both directions between segments would form segment loops which are not advantageous in the further design steps. In Figure 5. a., a SHSDG and its resulted segment structure is shown, where the modules are distributed by cuttings (dotted lines) so that data links arise between the segments (thick edges) in both directions. Such *not allowable* cuttings in SHSDG should be avoided by the decomposition algorithm. It is the same problem that

Figure 5: Illustration of allowable and not allowable cuttings

occurred in [11], where the not allowable cuttings are called as 'illegal partitions'. In Figure 5. b., the same SHSDG is distributed into segments having no data links in both direction between them. Therefore, no loops would arise with the segments A, B, and C.

The preparatory step of the decomposition algorithm is to find all advantageous allowable cuts (cutting places) and to map them into a *Cutting Matrix* (CM). Generating the CM is performed by the algoritm CMGEN. After this preparatory step, the aim of the decomposition algorithm is to select from the allowable cuts by attempting to optimize according to some parameters given in advance. This can be performed by an algorithm shown in the next section. In this section, the algorithm CMGEN is described. The algorithm is similar to finding the minimal cut or the maximal flow in a weighted graph [36, 37, 38, 39]. While these algorithms are dedicated for distributing the graph into two segments, CMGEN is able to prepare the distribution into more segments generated by allowable cutting places only.

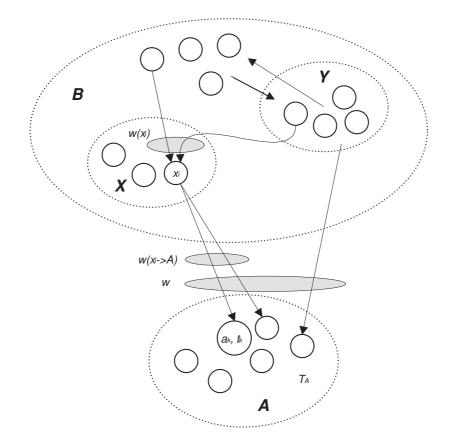

The algorithm allows considering the communication burden (time-demand) between segments during the mapping procedure by assigning proper weights to the data links. It permits that always those allowable cuts are chosen for mapping into the CM which have the smallest weight, if there are more possibilities. Weights may characterize the data quantity to be transferred on the data links, but the weight definitions and assignment can be changed depending on the various implementations of the communication between the processing units in the target system. Definitions and main steps of algorithm CMGEN are summarized in Figure 7, based on the illustration in Figure 6.

The algorithm uses the following definitions. Let those nodes of the SHSDG, which have no predecessor or successor nodes, be called input nodes and output nodes, respectively. For example, an input node is node  $m_1$  and an output is node  $m_{12}$  in Figure 3. Let A and B denote disjoint subsets of all nodes in SHSDG. Let two disjoint subsets (X and Y) be generated in B according to the following properties:

- Subset X contains all nodes of B which send data only to nodes of set A.

- Subset Y contains all nodes of B which send data to nodes both of sets B and A.

- The remaining nodes of *B* are assumed to send data only to the nodes of set *B*.

Let the following notations be introduced:

- $x_i$  and  $y_j$  denote the elements of sets X and Y, respectively

- $w(x_i)$  denotes the sum of weights of all data links having the drain node  $x_i$

- $w(x_i \rightarrow A)$  denotes the sum of weights of all data links having the source node  $x_i$

- w denotes the sum of weights of all data links from set B to set A

- $t_k$  denotes the estimated execution time of  $a_k$ , where  $a_k$  is an element of set A

- $T_A$  denotes the estimated execution time of the actual node set A. It is defined as the sum of all  $t_k$ -s.

The above properties and notations are illustrated in Figure 6. The CM is generated according to Figure 7. Initially, set A contains the output nodes only and set B contains the rest of the nodes. This situation is represented in CM by mapping all output nodes into the first row indicating that this cut generates two segments by cutting at the input data links of all output nodes. This cutting is always trivially allowable because the output nodes have no output data links to other nodes. Further on, each node  $x_i$  is relocated one by one from X to A. Since set X contains nodes sending data only to A, all nodes of the actual Asend data only inside A. If there would be a node that has both outputs leading out of the graph, and outputs that are inputs to other nodes inside the graph, the algorithm would create a not allowable cut. However, these type of nodes can not exist in the SHSDG, because fictive output nodes are inserted during the

Figure 6: Illustration for the CMGEN algorithm

#### Input:

G directed graph

#### Output:

Matrix containing possible cutting places

#### **Definitions**:

G: set of nodes of the input graph A, B: subsets of G where B = G - A

k : outputs of the graph

$X \in B, \{X\}_{B->A}$ : all nodes of B which send data only to nodes of set A $Y \in B, \{Y\}_{B->A}$ : all nodes of B which send data to both nodes of set Band A

$w(x_i \to A)$ : sum of weights of all data links having the source node  $x_i$  $w(x_i)$ : sum of weights of all data links having the drain node  $x_i$  $t_k$ : estimated execution time of  $a_k, a_k \in A$  $T_A: \Sigma(t_k), a_k \in A$ z : cycle parameter, indicates the row numbers in the matrix  $\Delta w(x_i) = w(x_{i->A}) - w(x_i)$ w: denotes the sum of weights of all data links from set B to set A CMGEN algorithm:  $1 A \leftarrow \{k\}$ 2 put  $\{k\}$  into the 1st row of the matrix  $3 \ z = 2$ 4 while  $(B \neq 0)$  $5 \{$  $A \leftarrow \{x_i\}$ , where  $x_i \in X$  and for any  $x_j \in B$ :  $\Delta w(x_i) \ge \Delta w(x_j)$ 6 7count  $T_A = \Sigma(t_k)$ put z into row z of the matrix 8 put  $x_i$  into row z of the matrix 9 10 put  $T_A$  into row z of the matrix  $11 \quad z + +$ 12 }

Figure 7: The definitions and main steps of algorithm CMGEN

generation procedure as described in Section 3. Therefore, the cuts formed by relocating nodes from X to A are always allowable ones. The relocated node is mapped into the next row of CM. Thus, each row of CM represents an allowable separation of SHSDG into two segments. After each relocation, sets A, B, X, Y, and all weights are actualized and recalculated. If the actual set X contains more nodes, then the selection of  $x_i$  for relocating is made by considering the effect on the communication burden between the segments generated by the relocation step. This effect can be characterized by evaluating the change in the value of w after relocating  $x_i$ . The aim is to relocate always that  $x_i$  which results in the greatest decrease in the new value of w. According to the notations,  $w(x_i \to A)$  reduces the value of w, because after the relocation  $x_i$  will be already in set A. In contrary,  $w(x_i)$  increases the value of w, because all data links having the drain node  $x_i$  will appear between the set B and A, i.e. between segments. Thus, the change of w caused by relocating  $x_i$  can be expressed as follows:

$$w_{new} = w_{old} - w(x_i \to A) + w(x_i),$$

where  $w_{old}$  and  $w_{new}$  are the values of w before and after the relocation, respectively. By introducing  $\Delta w(x_i) = w(x_i \to A) - w(x_i)$ ,

$$w_{new} = w_{old} - \Delta w(x_i).$$

Thus, that  $x_i$  should be selected, for which  $\Delta w(x_i)$  is the greatest. (In the case of identical greatest  $\Delta w(x_i)$  values, the selection might be arbitrary at such simple weight definition).

By continuing the above selection, relocation and recalculation steps, set B will become empty sooner or later, because all outputs of the graph are put into set A at the initialization step of algorithm CMGEN. Therefore, the algorithm relocates each node into set A sooner or later. At this point, the algorithm for mapping into CM ends. Each row represents an allowable cut in SHSDG and the actual contents of sets A and B define the two segments separated by this cut. Because of the above selection strategy for relocating, CM generally does not contain all allowable cuts. Namely, also an allowable cut would be obtained by relocating a node  $x_i$  having not the maximal value of  $\Delta w(x_i)$ . In this case, the order of  $x_i$ -s would change in CM, and so the content of separated segments may also be affected. However, such allowable cuts do not appear in CM, if the relocating is always performed according to the maximal value of  $\Delta w(x_i)$ .

The structure of CM generated by the algorithm CMGEN is illustrated in Figure 8. The first column contains row numbers, the second column identifies the node which is selected for relocation from set X to set A in that step, the third column contains the estimated execution times of the actual set A resulted by summing the execution times of all nodes in A. This is a worst case estimation, since the decreasing effect of the possible parallel or alternative node executions (e.g. conditional branches) are not considered at this point for the sake of simplicity. Of course, more accurate estimation could be done by considering possible parallel or alternative node executions.

As a summary, the properties of the CM are as follow:

|           | num | relocated node | Estimated<br>execution<br>times |

|-----------|-----|----------------|---------------------------------|

| ſ         | 1   | {node 1b}      | T <sub>1b</sub>                 |

| Segment 1 | 2   | {node c}       | T <sub>c</sub>                  |

| Ŭ ]       | :   |                | ÷                               |

|           | е   | {node e}       | T <sub>e</sub>                  |

|           | e+1 | {node e+1}     | T <sub>e+1</sub>                |

| Segment 2 | ÷   | ÷              | :                               |

|           | r   | {node r}       | T,                              |

|           | r+1 | {node r+1}     | T <sub>r+1</sub>                |

| Segment 3 | ÷   | ÷              | :                               |

|           | t   | {node t}       | T <sub>t</sub>                  |

| ſ         |     |                | :                               |

| Segment 4 | Z   | {node z}       | Tz                              |

Figure 8: The structure of the cutting matrix (CM) and an illustration for the segmentation

- Each row of the CM represents an allowable cutting place.

- The first row identifies all output nodes of SHSDG.

- Input nodes can occur in any rows except in the first one.

- A cut (a row) in CM identifies a decomposition of SHSDG by distributing its nodes into two segments composed by the nodes in rows above (set A) and by the nodes below (set B) this cut, respectively.

By the help of the CM, the distribution of the SHSDG into segments can be performed. In the next step of the decomposition algorithm, an optimal selection from the advantageous allowable cutting places is attempted. The desired number of the resulting segments (P) can be given in advance. It means that P sets of rows should be generated in CM. In Figure 8, P = 4 is assumed, so three rows of the CM as cutting places are to be determined. An assumed decomposition result is illustrated by the thick horizontal lines in Figure 8 as selected cutting places. The nodes contained by the four segments are assigned by the selected three cutting places. An algorithm for selecting the cutting places is described in the next section.

## 5 The decomposition algorithm

Various practical conditions may be formulated to influence the decomposition procedure. One of the practical aims can be to prescribe the desired maximal number (P) of segments as an input parameter for the decomposition algorithm. Let  $S : \{s_1, s_2, \ldots, s_k\}$  denote the set of segments resulted by the decomposition algorithm. Besides k = P, the algorithm may propose a segmentation in which k < P, if the same or more beneficial solution can be achieved by generating less segments. The k > P case is not considered, since there always must be an upper limit for the number of segments. Usually this upper limit is defined by the number of available processing units for the implementation. Just this could be the reason why P may be prescribed as input parameter in advance.

In order to attempt an optimal segmentation in some sense, a cost function should be constructed that enables to apply a global optimization algorithm. Applying global optimization algorithms (e.g. ant colony optimization [40] or genetic algorithm [41]) is not unfamiliar in partitioning problems, especially in hardware software codesign. The cost function should be defined by considering the purpose of the segmentation and the properties of the target system. In the decomposition algorithm proposed in this paper, two alternatives for the cost function are shown as examples.

The first alternative is to consider the processing units in which the segments will be implemented. Different processing units may have different communication speed, execution speed and capacity. Let a single unique identifying integer from the set  $\{1, 2, \ldots, P\}$  be assigned to each processing units that is available to implement the segments. Hereby, the assignment of available processing units to segments can be formally represented by the assignment identifying set of integers  $U : \{u_1, u_2, \ldots, u_P\}$ . For example, if segment  $s_i$  is assigned to processing unit 2, then  $u_i = 2$ . Each processing unit is characterized by the following attributes: the speed of execution, the maximal execution time of the segment the can be allocated into the processing unit (also called the capability of the processing unit), and the communication cost between each pair of processing units. Identical types among the available processing units are represented by identical attributes. For attempting to find an optimal solution, the most advantageous processing unit should be selected for each segment. The algorithm presented in this paper does not assign more segments to the same processing unit. Otherwise, the graph of the segments might be affected, even loops might arise in the resulted architecture similarly to the not allowed cuts. Thus  $u_i = u_i$  cannot occur. In the second alternative, only the segmentation is performed without assigning the segments to processing units. This alternative is more suitable for applying a HLS tool after the segmentation in order to allocate the segments for establishing advantageous pipeline architecture. In this case, the optimization is attempted by choosing a Pareto-optimal solution that varies between fast communication and fast execution of the segments. The two alternatives outlined above and the relation between P and k represent four cases:

- Case 1: Segmentation and assignment to processing units, k = P only.

- Case 2: Segmentation and assignment to processing units, k < P also allowed.

- Case 3: Segmentation only, k = P only.

- Case 4: Segmentation only, k < P also allowed.

The decomposition algorithm proposed in this paper is illustrated for these four cases as a framework. The first step is to formulate a proper cost function for attempting to find the optimal segmentation in each of the four cases. As an example, let the cost function (f) be introduced as follows:

$$f = \sum_{i=1}^{P-1} \left( G_{u_i}^{-1} T_i + \max_j \left( C_{u_i \to u_j} Com_{i \to j} \right) + \sigma\left(i, u_i\right) \right) + G_{u_P}^{-1} T_P + \sigma\left(P, u_P\right)$$

where

- $u_i$ : is the identifying integer of the processing unit assigned to segment  $s_i$

- $G_{u_i}$ : is the processing speed of the processing unit identified by  $u_i$ ,

- $T_i$ : is the execution time of segment  $s_i$ ,

- $C_{u_i \to u_j}$ : is the communication cost between processing units identified by  $u_i$  and  $u_j$ ,

- $Com_{i \to j}$ : is the communication burden (number of bits transferred in the examples) between segments  $s_i$  and  $s_j$ ,

- $\sigma(i, u_i)$ : is an overfill function for the processing unit identified by  $u_i$  assigned to  $s_i$ .

Further on, all values of execution time, processing speed and communication time are handled as relative values without considering the dimensions. Note that the sum in the cost function goes from 1 to P-1, since P-1 cuts are to be found for creating P segments. The capability of the processing unit is used to set a certain limit to the segment assigned to the processing unit. In this example, this measure is defined by the maximum value of the total execution time of the segment assigned to a given processing unit. Note that other limits may also be introduced instead of this, e.g. maximal memory size. Let the total execution time of segment  $s_i$  be denoted by  $T_i$ . Thus, an overfill function can be defined as follows:

$$\sigma(i, u_i) = \epsilon \left(T_i - Cap_{u_i}\right) \left(e^{\alpha \left(T_i - Cap_{u_i}\right)} - 1\right)$$

where  $Cap_{u_i}$  is a threshold defined for each processing unit  $u_i$  referred to as the capability of the processing unit, and  $\alpha$  is an appropriately chosen constant, while  $\epsilon(\cdot)$  stands for the Heaviside function. The Heaviside function provides the zero overfill function value, if the execution time of the segment to be implemented in  $u_i$  is under the limit defined by  $Cap_{u_i}$ , but increases exponentially, if this limit is exceeded. The function  $\sigma(i, u_i)$  could also be defined as an ideal one that provides zero, if the execution time of  $s_i$  is less than or equal to  $Cap_{u_i}$ , and provides an infinite value, if the the execution time of  $s_i$  exceeds this limit. The function used here approximates this ideal function by a continuous change. The parameter  $\alpha$  determines the approximation distance between the ideal function and the continuous one. The greater the  $\alpha$  is, the closer the function is to the ideal one. The reason of using a continuous function is to help the convergence of the gradient-like optimum search algorithms.

The cost function basically considers the execution times of the resulting segments that highly depend on the speed of the processing units in which the segments are implemented. The communication cost is added to the execution time inspiring the fact that the communication affects the execution time of the whole SP. The third component in the cost function represents the size-limits of the segments for avoiding useless solutions.

Minimizing the above cost function results in minimal latency, since it is the sum of relative time values for all segments. The minimization of the pipeline restart time will be attempted by the HLS tool, as it is shown in the further sections.

In this paper, the optimization is attempted to be solved by applying a Single-population Genetic Algorithm (SGA) with real population as an example. Each individual is composed of 2P - 1 genes, as follows:

$$\begin{vmatrix} c_1 & c_2 & \dots & c_{P-1} & u_1 & u_2 & \dots & u_P \end{vmatrix}$$

The first P-1 genes determine the place of the cuts (the rows of the CM), i.e.  $c_i$  determines where segments  $s_i$  and  $s_{i+1}$  are separated. The values of  $c_i$  are chosen from the set  $\{1, \ldots, J-1\}$ , where J is the number of rows of the cutting matrix CM. Note that P has to be chosen such that  $P \leq J$  must hold. This may be a limit in prescribing the value of P and it turns out only at this stage. The set of nodes contained in a segment are determined by the second column of the CM that contains the relocated nodes. The first segment is composed of the nodes that are between the  $1^{st}$  row and the  $c_1$ -th row of CM ( $c_1 = e$  in the example in Figure 8), the second segment is composed of the nodes that are between  $(c_1 + 1)$ -th row and  $c_2$ -th row of CM  $(c_2 = r \text{ in the example in Figure})$ 8), and so on. The last segment is composed of the nodes that are between the  $(c_{P-1}+1)$ -th row and the J-th row of the cutting matrix. The process of creating segments requires that  $1 \leq c_1 < c_2 < \ldots < c_{P-1} < J$  must hold. Each of the last P genes determines a processing unit  $u_i$ , in which segment  $s_i$ is implemented, respectively. As the formal representation of the identifying integers, the value of  $u_i$  is chosen from the set  $\{1, 2, \ldots, P\}$ , and  $u_i \neq u_j$  must hold for all  $i \neq j$ , and so the last P genes are permutations of the elements of the integers  $1, 2, \ldots, P$ .

In the standard genetic algorithm applied in this paper, only the recombination and mutation operators have to be changed to suit the problem. The recombination of these individuals requires a careful treatment. The first P-1 genes are recombined using standard intermediate recombination, however the last P genes cannot be generated by this method, since the last P genes need to be the permutations of the finite series  $1, 2, \ldots, P$ , i.e. the identifiers of the processing units. If intermediate recombination were applied, then the result would not necessarily be a permutation of that series. Therefore, the recombination of the last P genes is done by creating two offsprings with the same genes at the first P-1 position, but different genes at the last P position inherited from both parents. Then, another group of offspring is created by adding random permutations at the last P genes. The best offspring is chosen according to the cost function. The mutation operator acts similarly. The first P-1 genes are mutated in standard manner, however the last P genes are mutated by creating a random permutation of the series  $1, 2, \ldots, P$ .

The minimal value of the cost function is the upper limit of the latency of the best individual, if the capability limits of the processing units are not exceeded. Namely, the latency is the sum of the execution and communication times.

The decomposition framework presented above is suitable for handling each of the four cases. For example, a simple modification in the procedure can make it suitable for Cases 2 and 4, when the result may contain less than P segments, if the minimization of the cost function were more beneficial in this way. In order to ensure this feature of the optimization process, the value of zero can be assigned to any of the last P genes of the individuals. The zero value of a gene in one of the last P places means that the segment is not realized at all, thus it does not exist. This zero value can be interpreted as a fictive processing unit, with zero processing speed ( $G_0 = 0$ ), zero communication cost ( $C_{0\to u_j} = 0$ ), and infinite capability threshold ( $Cap_0 = \infty$ ). During the optimization procedure, this zero assignment can be attempted and evaluated for any number of genes at the last P places of the individuals to simulate as if the corresponding  $c_i$ genes were neglected as cutting places.

In Cases 3 and 4, the result of the segmentation serves as input for a HLS tool. Therefore, the types and the properties of the processing units will be determined by the allocation result of a HLS tool. The cost function applied above for a general case can be fitted easily to these cases by defining formally the same type for each processing unit. The speed and the communication burden of this single type processing unit determine the trade-off between optimizing the minimal execution time of a segment and the communication time between segments. The capability of the single type processing unit serves as an upper bound on the maximal execution time of a segment in this case.

## 6 Experimental results

The main steps and design cases of the method described in the previous sections are illustrated on an example C code used in audio synthesis. The program consists of three functions, the main function and two other user defined functions. The nodes associated to the commands of the program code are denoted in the comments. Pure variable declarations are handled as the inputs of the program. Thus the program code (called SP in the previous sections) is as follows:

```

#include<stdio.h>

#include<math.h>

11

//Node 11

//Node 12

//Node 13

void genSweep(float *buffer,long numSamples,int sampleRate,...

//Node 14

//Node 15

float minFreq,float maxFreq){

float start=2.0*3.14*minFreq; //Node 16

float stop=2.0*3.14*maxFreq; //Node 17

float tmp1=log(stop/start); //Node 18

long s=0; //Node 19

while(s < numSamples) //Node 20</pre>

{

float t;

t=(float)s/numSamples;

float tmp2;

tmp2=exp(t*tmp1)-1.0;

buffer[s]=sin((start*(float)numSamples*tmp2)/...

((float)sampleRate*tmp1));

s++;

}

// Node 21 is a fictive out node

}

11

//Node 22

//Node 23

//Node 24

void fadeInOut(float *buffer, long numSamples, int sampleRate,...

//Node 25

float fadeTime)

{

long numFadeSamples=fadeTime*sampleRate; //Node 26

if(numFadeSamples > numSamples) //Node 27

// Node 28 for branch node

{

numFadeSamples=numSamples; //Node 29

}

long s=0; //Node 30

while(s < numFadeSamples) //Node 31</pre>

ſ

float weight;

weight=0.5*(1-cos(3.14*s/(numFadeSamples-1)));

buffer[s]=buffer[s] * weight;

buffer[numSamples-(s+1)]=buffer[numSamples-(s+1)]*weight;

s++;

}

```

```

//Node 32 is a fictive out node

}

11

//Node 4

//Node 1

//Node 2

float* top_module(float *buffer, int sampleRate, float duration,..

//Node 5

//Node 6

//Node 7

float minfreq,float maxfreq, float fadetime) {

long numSamples=duration*sampleRate; //Node 3

genSweep(buffer,numSamples,sampleRate,minfreq,maxfreq);//Node 8

fadeInOut(buffer,numSamples,sampleRate,fadetime); //Node 9

return buffer; //Node 10

}

// main function for the test on CPU

int main() {

float buffer[1];

top_module(buffer, 1, 1, 440, 4400, 10);

for (int i=0; i<1; i++)</pre>

ł

printf("%f\n",buffer[i]);

}

}

```

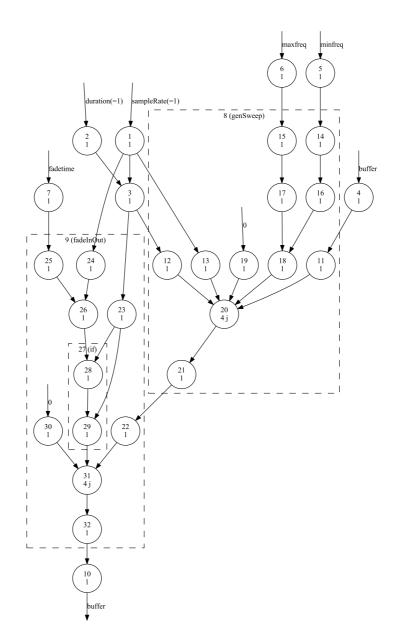

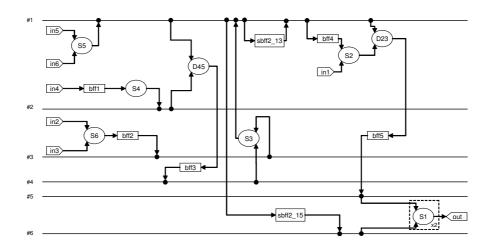

The SHSDG belonging to the highest (in this case the  $3^{rd}$ ) hierarchy level is shown in Figure 9. The labels in the nodes consist of two rows: the first one is the identifying index of the node, and the second one refers to the estimated execution time of the node. In this simple illustration, the estimated execution times are assumed to be 1 for each node which does not represent a loop. The nodes representing loops (nodes 20 and 31) are assumed to have the estimated execution times determined by the sum of execution times of the nodes forming the loop (as if the loops were executed only once). Of course, this simplified estimation is made only for demonstrating formally the steps of the synthesis framework presented in this paper. Realistic estimations might be elaborated by considering the type and character of the loop. Such considerations and the loop handling are crucial in high level synthesis [1], [42], [43], [44]. To develop loop rules dedicated specifically to the synthesis method presented in this paper is one of the aims for further research. In this particular case, the number of loop cycle depends on input variables *duration* and *sampleRate*, these are assumed to be 1. The execution time of both loops is 4i (since there are 4 nodes in the loop), where j = duration \* sampleRate. In this example j = 1. This simplification would be justified, if the loop in the C code is assumed to get all the data in the buffer array variable, and each loop cycle is executed on a single element of the array independently. In this case, the whole buffer array can be loaded and handled in pipeline mode. In consequence, the whole program would be executed for each element of the buffer. Thus, some program parts (which should be executed only once for a specific buffer array) would be executed

multiple times (e.g. nodes 5, 6, 14, 15, 16, 17, 18 in Figure 9). However, this solution implies that the size of the buffer array does not affect the structure of the resulting system, but it determines the pipeline restart time.

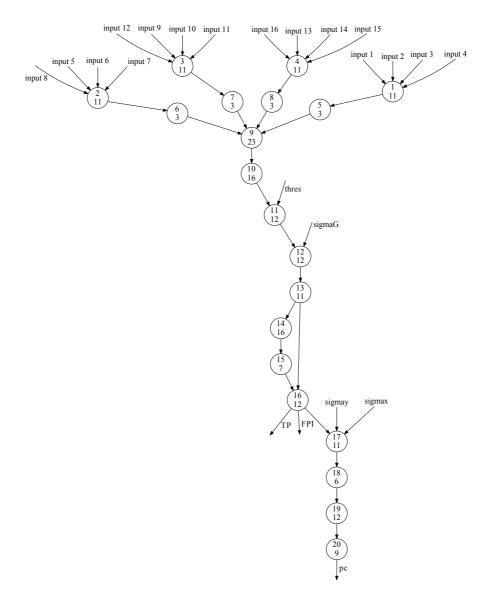

The Cutting Matrix resulting from the SHSDG can be seen in Figure 10. The first column of the matrix (num) contains the identifying indices of the cutting places. The  $c_i$  genes in the genetic algorithm refer to these indices. The second column contains the nodes that are actually relocated to the set containing the nodes above a given index in the matrix. The third column contains the cumulated estimated execution times of the nodes forming the segment above the cutting place. These cumulated estimated execution times are recalculated at each step by adding the estimated execution time of the node defined in the second column. For the sake of simplicity, it is a worst case estimation, since it does not consider the possible parallel or alternative node executions.

Further on, some results are shown in the four design cases defined in the previous section.

#### Case 1

Let two different types of processing units be assumed, and they will be called hardware and software. Thus, this problem is analogous to the well-known hardware-software splitting. Let the relative properties (represented by integers) of the units be assumed as follows:

- The processing speed of the software is  $G_s = 1$

- The processing speed of the hardware is  $G_h = 6$

- The communication cost between hardware and software is  $C_{h\to s} = 3$

- The communication cost between two hardware is  $C_{h \to h} = 2$

- The communication cost between two software is  $C_{s \to s} = 5$

- The capability of the software is  $Cap_s = 15$

- The capability of the hardware is  $Cap_h = 10$

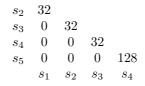

The decomposition is done first with k = P, using 3 software and 3 hardware units, i.e. P = 6. The result of the decomposition is represented by an adjacency half matrix in Figure 11. Each row and each column is labeled by a segment  $s_i$ . The number in the cell corresponding to  $s_j$  and to  $s_k$  represents the number of bits that need to be transferred from segment  $s_j$  to segment  $s_k$ . The communication cost between the processing units is not indicated in the adjacency half matrix.

Figure 9: The SHSDG of the program code on the highest hierarchy level

| num | relocated node | Estimated       |

|-----|----------------|-----------------|

|     |                | execution times |

| 1   | 10             | 1               |

| 2   | 32             | 2               |

| 3   | 31             | 6               |

| 4   | 30             | 7               |

| 5   | 29             | 8               |

| 6   | 22             | 9               |

| 7   | 21             | 10              |

| 8   | 28             | 11              |

| 9   | 23             | 12              |

| 10  | 26             | 13              |

| 11  | 25             | 14              |

| 12  | 7              | 15              |

| 13  | 24             | 16              |

| 14  | 20             | 20              |

| 15  | 19             | 21              |

| 16  | 11             | 22              |

| 17  | 4              | 23              |

| 18  | 12             | 24              |

| 19  | 3              | 25              |

| 20  | 2              | 26              |

| 21  | 13             | 27              |

| 22  | 1              | 28              |

| 23  | 18             | 29              |

| 24  | 17             | 30              |

| 25  | 16             | 31              |

| 26  | 15             | 32              |

| 27  | 6              | 33              |

| 28  | 14             | 34              |

| 29  | 5              | 35              |

Figure 10: The Cutting Matrix of the SHSDG in Figure 9

| $s_2$ | 32    |       |       |       |       |

|-------|-------|-------|-------|-------|-------|

| $s_3$ | 48    | 0     |       |       |       |

| $s_4$ | 0     | 0     | 32    |       |       |

| $s_5$ | 32    | 0     | 64    | 0     |       |

| $s_6$ | 0     | 0     | 144   | 0     | 0     |

|       | $s_1$ | $s_2$ | $s_3$ | $s_4$ | $s_5$ |

Figure 11: The adjacency half matrix of the decomposition result with  ${\cal P}=k=6,\,3$  hardware and 3 software units

Figure 12: The result of the decomposition for Case 1, using 3 software and 3 hardware units

The resulting segments contain the following nodes (with execution times  $T_i$ ):

| $s_1 = \{ 10 \}$ | $32 \ 31 \ 30 \ 29 \ 2$ | $2 \ 21 \ 28 \ 23$ | 26 } $T_1 = 13$ |

|------------------|-------------------------|--------------------|-----------------|

| $s_2 = \{ 25 \}$ | 7 }                     |                    | $T_2 = 2$       |

| $s_3 = \{ 24 \}$ | $20  19  11 \}$         |                    | $T_{3} = 7$     |

| $s_4 = \{ 4 \}$  |                         |                    | $T_4 = 1$       |

| $s_5 = \{ 12 \}$ | $3 \ 2 \ 13 \ 1 \}$     |                    | $T_5 = 5$       |

| $s_6 = \{ 18 \}$ | $17 \ 16 \ 15 \ 6 \ 14$ | $5$ }              | $T_{6} = 7$     |

Segments 1, 2 and 4 are implemented in software, and segments 3, 5 and 6 are implemented in hardware processing units. The best value of the cost function delivered by the decomposition algorithm is f = 508. The result of the decomposition is also depicted as a directed graph in Figure 12. The segments are the nodes of the graph. The labels of the nodes consist of three rows. The first row is the name of the processing unit type implementing the segment. The second row is the list of SHSDG nodes allocated into the segment, and the last row is the execution time divided by the relative processing speed of the processing unit implementing the segment.

| $s_2$ | 48    |       |       |

|-------|-------|-------|-------|

| $s_3$ | 32    | 64    |       |

| $s_4$ | 0     | 144   | 0     |

|       | $s_1$ | $s_2$ | $s_3$ |

Figure 13: The adjacency half matrix of the decomposition result with k < P = 6 (3 hardware and 3 software units), the result consists of 3 hardware and 1 software units.

#### Case 2

In this case, k < P is also allowed. Let the number and types of processing units be assumed as in Case 1. Let the cost function be modified by an extra  $+\lambda k$  term, where  $\lambda > 0$  is a parameter for quantifying how small number of segments would be favored by the user. By executing the decomposition for various values of parameter  $\lambda$ , the user may tune the result according to several requirements in the target system. Thus the cost function used in Case 2 (and also in Case 4 later on) is

$$f = \sum_{i=1}^{k-1} \left( G_{u_i}^{-1} T_i + \max_j \left( C_{u_i \to u_j} Com_{i \to j} \right) + \sigma\left(i, u_i\right) \right) + G_{u_k}^{-1} T_k + \sigma\left(k, u_k\right) + \lambda k$$

where the indices go from 1 to k instead of 1 to P and the extra  $+\lambda k$  term is added.

For example, let the effects of  $\lambda = 90$  be examined. The result of the decomposition is 4 segments, 3 of them implemented in hardware, and one of them in software units. The adjacency half matrix is shown in Figure 13.

The resulting segments contain the following nodes (with execution times  $T_i$ ):

| $s_1 = \{ 10 \}$ | $32 \ 31 \ 30$   | 29 22 | $21 \ 28$ | $23 \ 26$ | 25 | 7 } | $T_1 = 15$ |

|------------------|------------------|-------|-----------|-----------|----|-----|------------|

| $s_2 = \{ 24 \}$ | 20 19 11         | 4 }   |           |           |    |     | $T_2 = 8$  |

| $s_3 = \{ 12 \}$ | $3 \ 2 \ 13 \ 1$ | }     |           |           |    |     | $T_3 = 5$  |

| $s_4 = \{ 18 \}$ | $17 \ 16 \ 15$   | 6 14  | 5 }       |           |    |     | $T_4 = 7$  |

Segment 1 is implemented in software, segments 2, 3, and 4 are in hardware units. The resulted best value of the cost function is f = 941.1677 in this case. This value is greater than in Case 1, however the comparison would be realistic by considering the extra +90k component in the cost function. The impact of the original components can be compared, if 90k is subtracted from the value of the cost function obtained in this case, i.e.  $941.1677 - 90 \cdot 4 = 581.1677$ , which is greater than the cost value resulted in Case 1. Thus, Case 1 provides a better solution, if the effect of less processing units is not considered (see later Figure 18). For example, the decomposition algorithm has been executed in order to check whether k < P = 3 could offer a smaller value for the cost function. All of the three processing units are assumed to be hardware type now. The best

| $s_2$ | 32    |       |       |       |       |

|-------|-------|-------|-------|-------|-------|

| $s_3$ | 32    | 16    |       |       |       |

| $s_4$ | 0     | 0     | 32    |       |       |

| $s_5$ | 32    | 0     | 64    | 0     |       |

| $s_6$ | 0     | 0     | 144   | 0     | 0     |

|       | $s_1$ | $s_2$ | $s_3$ | $s_4$ | $s_5$ |

|       |       |       |       |       |       |

Figure 14: The adjacency half matrix of the result of decomposition in Case 3

result is obtained with 3 segments, i.e. k = P = 3 in this case. The resulted cost function value for comparison is  $1435 - 90 \cdot 3 = 1165$ . Thus, k = 4 in the former case seems to be a better solution, if the price of more processing units is not considered (see later Figure 18).

#### Case 3

In this case only segments are created without distributing them into processing units, because the result of the segmentation is assumed to be the input of a high-level synthesis tool in order to generate the proper allocation for establishing a pipeline system. The same cost function as the one defined in the previous section may be used also in this case. Formally only one type of fictive processing units is assumed. The ratio between the processing speed and the communication cost properties of this fictive processing unit is a tool to scale whether the low communication time or the low execution time is preferred. Let the processing speed of the processing unit be assumed  $G_s = 1$ , so the relative value of the communication cost defines this ratio. In this example the value of the communication cost is chosen as  $C_{s \to s} = 2$ . Let the capability of the fictive processing unit be  $Cap_s = 15$ . First the case k = P = 6 is considered. The resulted adjacency half matrix is shown in Figure 14. The resulted best value of the cost function is f = 419.

The segments contain the following nodes (with execution times  $T_i$ ):

| $s_1 = \{ 10 \}$ | $32  31  30  29  22  21  28  23 \}$ | $T_1 = 12$  |

|------------------|-------------------------------------|-------------|

| $s_2 = \{ 26 \}$ | $25 \ 7 \}$                         | $T_2 = 3$   |

| $s_3 = \{ 24 \}$ | $20  19 \}$                         | $T_3 = 6$   |

| $s_4 = \{ 11 \}$ | 4 }                                 | $T_4 = 2$   |

| $s_5 = \{ 12 \}$ | $3 \ 2 \ 13 \ 1 \}$                 | $T_{5} = 5$ |

| $s_6 = \{ 18 \}$ | $17 \ 16 \ 15 \ 6 \ 14 \ 5 $        | $T_{6} = 7$ |

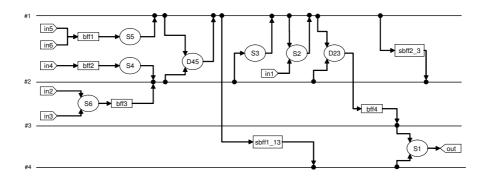

The result of the decomposition is depiceted as a directed graph in Figure 19.

#### Case 4

Now let k < P be also allowed. The cost function is modified by the  $+\lambda k$  term with  $\lambda = 90$  as in Case 2. The adjacency half matrix of the result is shown in Figure 15. The value obtained for the cost function is f = 773. In

| $s_2$ | 16    |       |       |

|-------|-------|-------|-------|

| $s_3$ | 64    | 16    |       |

| $s_4$ | 0     | 0     | 64    |

|       | $s_1$ | $s_2$ | $s_3$ |

Figure 15: The adjacency half matrix of the result of the decomposition in Case 4

order to compare this result with the value in Case 3, the cost function value obtained in Case 4 should be modified by subtracting the extra  $\lambda k$  term, i.e. it is 773 - 90  $\cdot$  3 = 503, that is greater than the result of Case 3. Thus, Case 3 provides a better solution, if the price gain of applying less processing units is not considered (see later Figure 18).

The segments contain the following nodes:

| $s_1 = \{ 10 \}$ | 32 | 31 | 30  | 29 | 22 | 21  | 28   | 23 | 26 | 25 | 7 } | $T_1 = 15$ |

|------------------|----|----|-----|----|----|-----|------|----|----|----|-----|------------|

| $s_2 = \{ 24 \}$ |    |    |     |    |    |     |      |    |    |    |     | $T_2 = 1$  |

| $s_3 = \{ 20 \}$ | 19 | 11 | 4   | 12 | 3  | 2 1 | .3 1 | 18 | 17 | 16 | }   | $T_3 = 15$ |

| $s_4 = \{ 15 \}$ | 6  | 14 | 5 } |    |    |     |      |    |    |    |     | $T_4 = 4$  |

### The effect of the segment weighting factor $\lambda$

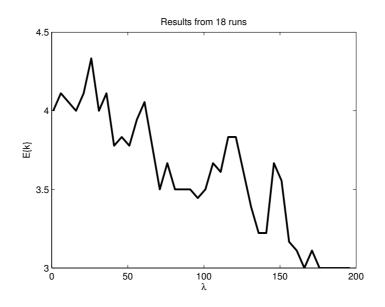

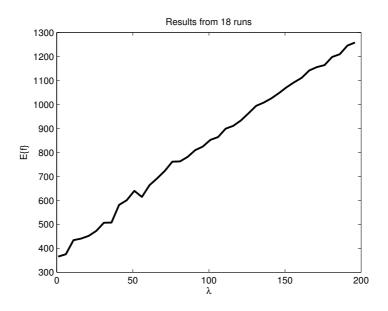

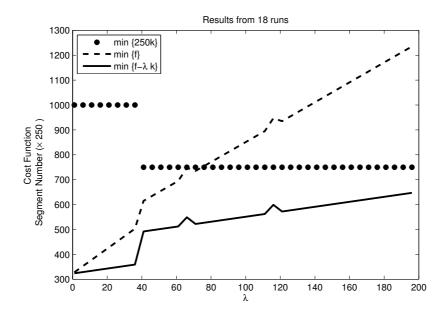

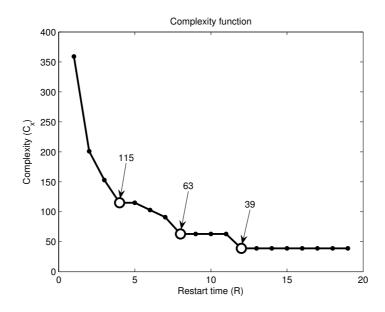

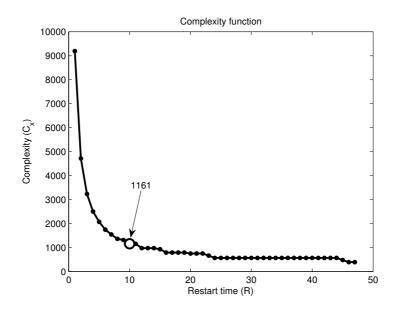

Most of the parameters in the decomposition algorithm (processing speed, communication cost, etc.) are the properties of the processing units. However, the role of parameter  $\lambda$  is to influence the algorithm by the user. There is no straightforward way to determine a proper value for  $\lambda$  weighting the number of segments during the decomposition, but some experimental considerations for a justifiable choice are presented in the following. Let the value of  $\lambda$  be varied from 1 to 196 with step size 5, thus  $\lambda = \{1, 6, 11, \ldots, 196\}$  in Case 4. Since the decomposition is based on a genetic algorithm with finite generations, the result may be different at each run. Therefore, the further illustration is based on the decomposition executed -for example- 18 times for each above value of  $\lambda$ . In Figures 16 and 17 the mean of the resulted number of program segments ( $E\{k\}$ ) and the mean of the cost function values ( $E\{f\}$ ) are depicted. Based on these figures, two trends can be observed by increasing the value of  $\lambda$ : the number of segments is decreasing, and the value of the cost function is increasing.

The first trend is trivial, since the greater the value of  $\lambda$  is, the less number of segments is favored in the decomposition. The second trend is also easy to explain, because increasing  $\lambda$  leads to worse results regarding the original optimality criteria components (execution times and communication costs). This is also evident in a multicriteria optimization, since the introduction of the new criterion weakens the effect of the other criteria.

Considering the above trends, the question can be formulated: how to find a beneficial value of  $\lambda$  and how to consider the effect of k? The mutual effect of these parameters can be observed by analyzing the results in Figure 18.